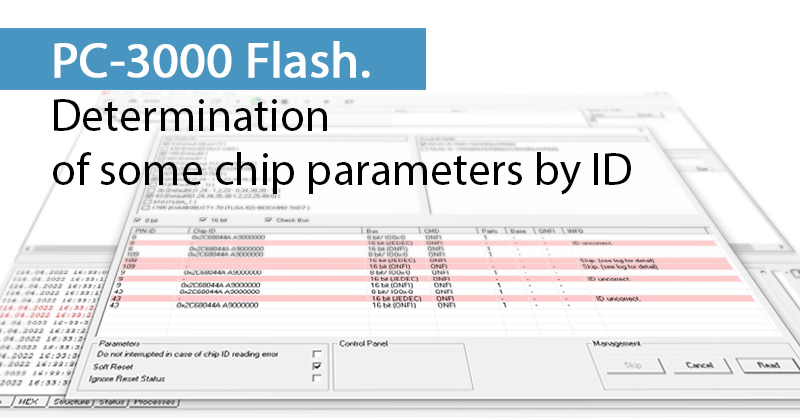

There are situations when you are reading a chip and see a detected Chip ID but it cannot be applied in the Task. As a result, it doesn’t allow to read the dump from the memory chip. Such behaviour may be if:

► The chip has physical damages or was overheated during the unsoldering process

► The memory chips reference book doesn’t have reading parameters for a certain Chip ID.

The information below will be useful when adding read parameters for new (unknown) memory chips and is intended for users who understand the main principles of NAND.

If you are new in NAND data recovery, we recommend studying these principles first.

Of course, you can try to find a datasheet for a certain memory chip and take reading parameters from there. But sometimes there is no possibility to find that datasheet or some parameters are missing there (not described).

Reading parameters detection is an investigation process and requires some specific knowledge. In this article, we’ll overview some ideas that can be helpful for you during this process. Anyway, we strongly recommend to contact our Technical Support Department if you get an unsupported NAND ID during your data recovery process.

Everyone is used to the fact that the chip ID consists of 4 bytes,

for example, 98DE9892, but, in fact, the full chip ID consists of 6 bytes, for example, 98DE9892-7656xxxx.

In this case, the PC-3000 Flash reader reads 8 bytes, but the last 2 bytes are not significant and won’t be considered.

The ID itself is necessary in order to distinguish one memory chip from another.

That’s why some basic characteristics of the chip are mentioned/stored in the ID, and some very important characteristics are also hidden in the 5th and 6th bytes.

First off, let’s take a look at which byte is responsible for what.

1 – Vendor ID, identification code of the manufacturer.

2 – Device ID, device identification code. But, in fact, the second byte of the ID has been responsible for other things for a long time.

3-6 – bytes defining the characteristics of the chip, which we will consider below.

First byte

It’s the Vendor ID byte which can be:

| 2C | Micron |

| 45 | Sandisk |

| 89 | Intel |

| 98 | Toshiba |

| AD | Hynix |

| EC | Samsung |

Second byte

It is the Device ID byte.

This byte is multifunctional, it is responsible for the capacity and, in some cases, for the bit depth of the memory chip.

Take a look at the table of dependence between the memory chip bank capacity and the second byte of the ID (the values are in Megabytes):

| E6 | 8 | 88 | 8192 | |

| 73 | 16 | D9 | 8192 | |

| 75 | 32 | DE | 8192 | |

| 66 | 64 | CE | 8192 | |

| 76 | 64 | EE | 8192 | |

| 79 | 128 | 64 | 8192 | |

| F1 | 128 | AE | 8192 | |

| 01 | 128 | 50 | 8192 | |

| AA | 256 | 4A | 16384 | |

| DA | 256 | A8 | 16384 | |

| CA | 256 | 84 | 16384 | |

| DC | 512 | 3A | 16384 | |

| CC | 512 | 4C | 16384 | |

| 29 | 512 | 1A | 16384 | |

| D3 | 1024 | 2D | 8192 | |

| 38 | 1024 | 4D | 8192 | |

| 48 | 2048 | 6D | 16384 | |

| D5 | 2048 | 78 | 4096 | |

| C5 | 2048 | 98 | 8192 | |

| 28 | 4096 | 3C | 32768 | |

| D7 | 4096 | C8 | 32768 | |

| 68 | 4096 | A4 | 32768 | |

| C7 | 4096 | 4E | 32768 | |

| E7 | 4096 | 3E | 65536 | |

| 44 | 4096 |

The table may not be complete, but it covers most of the modern memory chips.

Also, it is important to mention that the second byte of the Chip ID determines the capacity of one bank but not the entire chip.

In other words, if we have a Chip with a ‘DE’ second byte (8192), and at the same time this memory chip has 4 parts, then the total capacity of this memory chip is 32768.

But in the Reference book of the PC-3000 Flash tool, it is necessary to add the capacity of one Bank = 8192.

Also, the second byte allows determining the bus width of the memory chip (8bit or 16bit).

Let’s compare, for example, 2 bytes D7 and C7, in bit representation:

D7 = 11010111

C7 = 11000111

As we can see, the 4th bit has ‘1‘ value for D7 and ‘0‘ for C7.

This bit determines the chip width from manufacturers such as Toshiba and Sandisk, and in some cases from Samsung.

But at the same time, it is worth remembering that if the specified bit is = ‘0‘,

then this doesn’t mean that the bus is 16 bits. This is just a sign or we can say ‘support’ for a 16-bit operating mode, which in practice can turn out to be 16-8, for example.

Then there is the use of the lower 8 bits of the 16 bit data bus.

Moreover, if, for example, we have 2 memory chips:

45DE9892-7256

45CE9892-7256,

the reading parameters for both chips will be the same, except for the bus width.

Third byte

For most chips it is responsible for the number of LUNs and the type of memory.

For example, we have two memory chips:

98DE9892 and 98DE9532

first byte 98 – Toshiba

second byte DE – 8192 MB per bank

third byte binary representation:

98 = 10011000

95 = 10010101

The 2 last bits (blue) are responsible for the number of LUNs and take the following values:

0 0 – 1

0 1 – 2

1 0 – 4

1 1 – 8

This parameter is decisive for the special reading rules of the memory chip.

In the PC-3000 Flash software, in the special reading rules window, it is called “Number of planes”.

The next 2 bits (red) are responsible for the type and take the following values:

0 0 – SLC (2 Level Cell)

0 1 – MLC (4 Level Cell)

1 0 – TLC (8 Level Cell)

1 1 – QLC (16 Level Cell)

In accordance with the type of memory, potentially incorrect reading algorithms can be cut off, greatly reducing the time for refining the reading parameters.

The remaining bits of the third byte ID are reserved for some other things and their purpose is unknown.

The 4th and 5th bytes are strongly “Vendor-dependent”.

Each manufacturer determines parameters according to their own notion and the appointment may be different even within the same manufacturer but different generations of the chip.

Fifth byte

It has encoded the number of planes (not to be confused with the number of LUNs in the third byte).

The number of planes affects the presence, absence and type of the interleave (2-way (single) / 4-way (double)). We can get the information about the number of planes from bits 2 and 3 of the fifth byte of the ID:

0 0 – 1 plane

0 1 – 2 planes

1 0 – 4 planes

1 1 – 8 planes

Consider the example of two memory chips:

453C9A92-7Axxxxxx – the fifth byte in the ID = 7A, bin view 01111010,

according to table 10 = 4 planes,

98DE9892-76xxxxxx – the fifth byte in the ID = 76, bin view 01110110,

according to table 01 = 2 planes.

Thus, it is possible to foresee the presence of the interleave.

It is logical that if the chip has 2 or 4 planes, then it is likely that there will be an interleave – one if there are 2 planes, or two interleaves if there are 4 planes.

And it is also possible to foresee the absence of the interleave if the chip has a single plane.

Sixth byte

It is the last one that is of some interest in terms of determining the reading parameters.

It allows determining the reading mode: DDR or SDR.

For example, here are two Chip IDs:

98DE9892-7256

98DE9892-72D6

In the bit view:

56 = 01010110

D6 = 11010110

As we can see, only the first bit is different: 0 and 1.

This bit allows determining the reading mode.

1 = DDR

0 = SDR

But, sometimes, especially on old Toshiba and Sandisk memory chips, this bit defines the support of the DDR mode, and it can be enabled by a special command of the firmware. Though, by default, the reading mode is SDR.

It is also worth remembering that the rest of the parameters for the memory chip in such pairs as 98DE9892-7256 and 98DE9892-72D6 will be the same, except for the reading mode (SDR and DDR).

If you have questions regarding your data recovery cases, you’re welcome to address them to the ACE Lab Technical Support Department.

(9 votes, average: 4.11 out of 5)

(9 votes, average: 4.11 out of 5)